1. 关于iverilog

Icarus Verilog是一种Verilog仿真和综合工具,能够将基于Verilog(IEEE-1364)编写的源代码编译为某些目标格式。针对批处理仿真,编译器可生成一种名为" VVP "的中间组件;同时,自带GTKWave软件,可方便查看verilog/VHDL的仿真波形图。

相比FPGA大厂提供的复杂IDE,用户不仅要购买licence,而且需要花费不少时间熟悉操作方法;iverilog是一款轻量、免费、开源的Verilog编译器,且操作简单,通过“指令”操作,更贴近编译本质。

对于初学者,寻找一本好的教材,并基于iverilog平台熟悉例程,具有不错的学习效率。

2. 安装iverilog

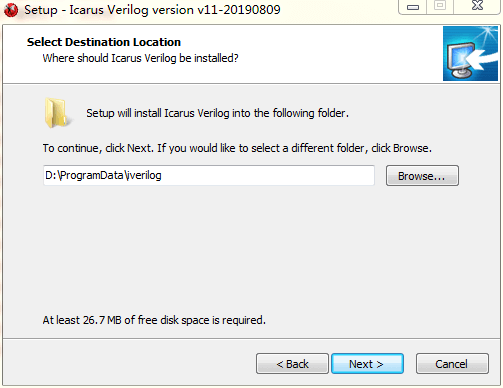

下载iverilog安装包完成后,直接双击安装即可(注意:路径不能有空格)。

目前最新版本:iverilog-v11-20190809-x64_setup.exe [17.0MB]

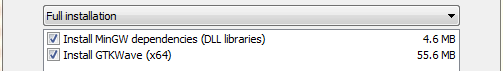

选择“全安装方式”,如下:

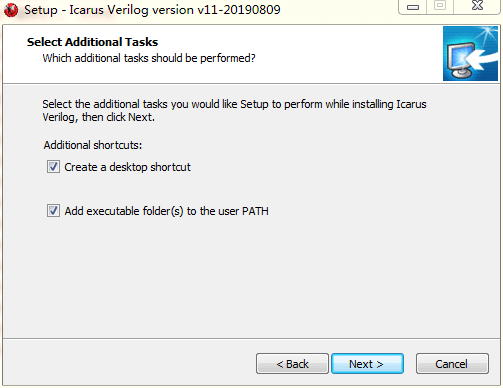

选择“添加到环境变量”,如下:

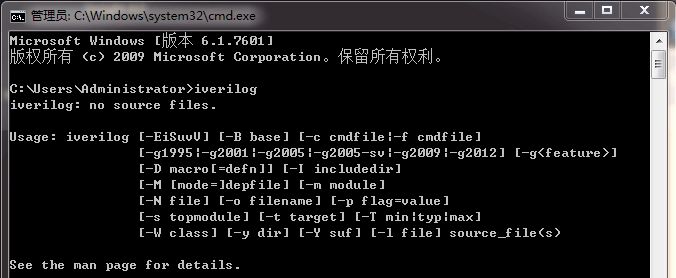

打开cmd终端,查看是否安装成功,如下:

用户也可选择Cygwin64 Terminal,具体安装方法见《Win7下类linux终端环境—Cygwin》

3. 编写源码及测试文件2020081514214651.zip

以计数器为例,源码文件(counter.v)如下:

module counter(irst, iclk, ocnt ); input irst, iclk; output reg [3:0] ocnt; always @ (posedge iclk) if(irst) ocnt <= 4'b0000; else ocnt <= ocnt + 1'b1; endmodule

对应的测试文件(counter_tb.v)如下:

module counter_tb; reg irst = 0; reg iclk = 0; wire [3:0] ocnt; initial begin irst = 1; #100; irst = 0; #300; $stop; #1000; $finish; end always begin #5 iclk = !iclk; end counter counter_test( .irst(irst), .iclk(iclk), .ocnt(ocnt) ); initial $monitor("At time %t, ocnt = %d", $time, ocnt); initial begin $dumpfile("counter_test.vcd"); $dumpvars(0, counter_test); end endmodule

4. 终端编译

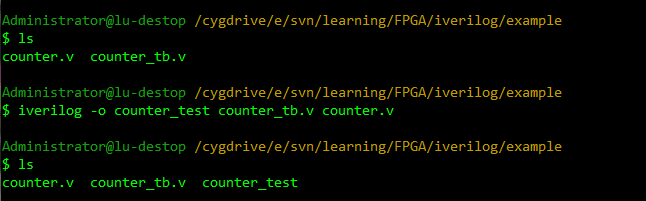

打开cmd终端 或 Cygwin64 Terminal ,依次输入以下指令,进行编译和执行。

(1)编译代码

iverilog -o counter_test counter_tb.v counter.v

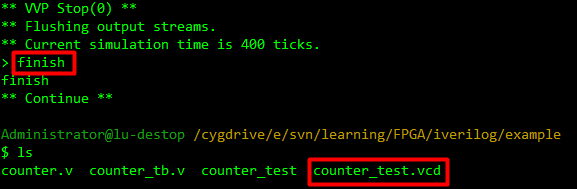

(2)生成.vcd文件

vvp counter_test

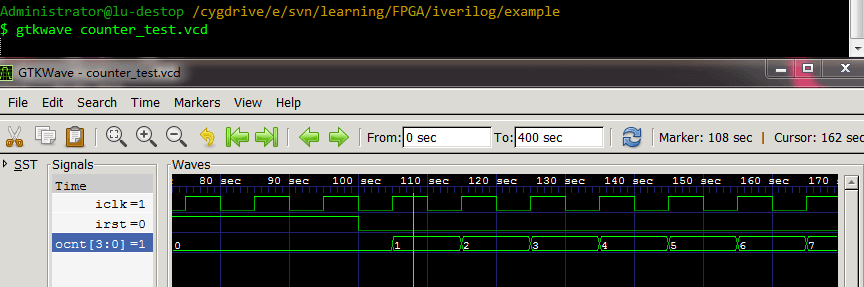

(3)gtkwave查看波形

gtkwave counter_test.vcd

5. 其它

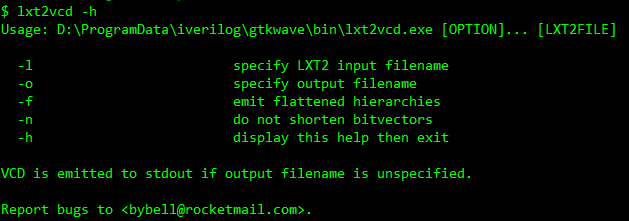

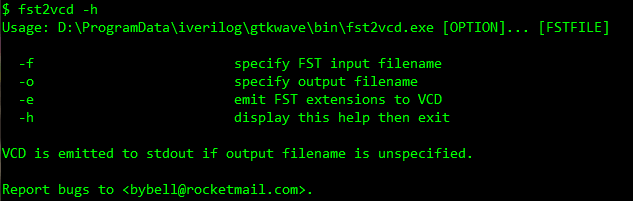

除以上功能外,ierilog也支持很多其它功能,如:文件格式转换功能等。如下:****