1. 手册汇总

Cortex-M0 的规格说明在许多ARM文档中都有所涉及。

- 《Cortex-M0 设备普通用户指南》(Generic User Guide)包括系统模型、指令集以及体系结构的一般信息。

- 《ARMv6-M体系结构参考手册》(ARMv6-M Architecture Reference Manual)关于指令集、系统模型和其它内容的详细信息。

- 《Cortex-M0技术参考手册》(Cortex-M0 Technical Reference Manual)

DUI0497A_cortex_m0_r0p0_generic_ug.pdf

DDI0419C_arm_architecture_v6m_reference_manual.pdf

2. ARM 体系架构

ARM 每发布一次新产品,都会在架构说明里面增加新的指令和架构特性,这样一来,架构就会产生众多版本。架构版本号和处理器独立命令,一种处理器系列可能会包含多个架构。例如:早期的 ARM9 处理器(ARM920T 和 ARM922T)都是基于 4T 版本的架构,而新版本的 ARM9 处理器(ARM926EJ-S、ARM946E 和 ARM966E等)都是基于 5TE 的版本。

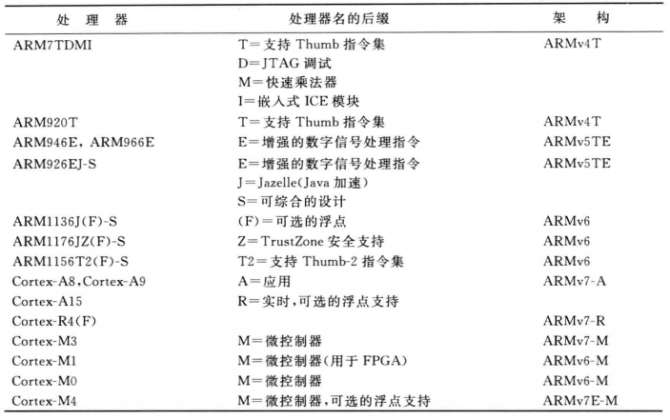

常用 ARM 处理器及对应的架构版本,如下图:

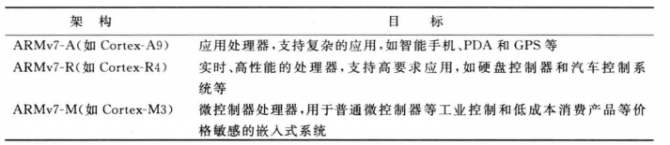

ARM11 处理器系列发布以后,在最高级别 ARM 处理器中使用的一些新的特性和技术,在低成本或高集成度的设备中也有体现。例如:Thumb-2 指令集对运行在 Thumb 状态的处理器有了性能的提升,CoreSight Debug 架构的可扩展调试技术,比以前的解决方案提供了更好的调试功能。因此,从第 7 个版本开始,架构被分为 3 类,分别对应不同的应用领域。新一代的处理器被称为 Cortex,后缀表示不同设计及其归属的类别。

ARM 处理器及架构命名,如下图:

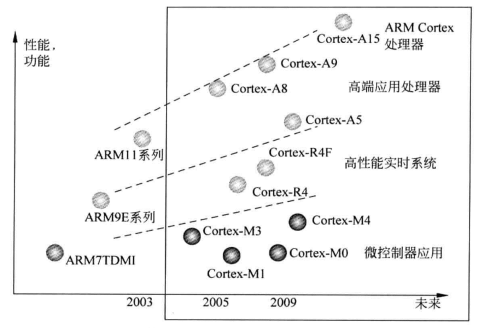

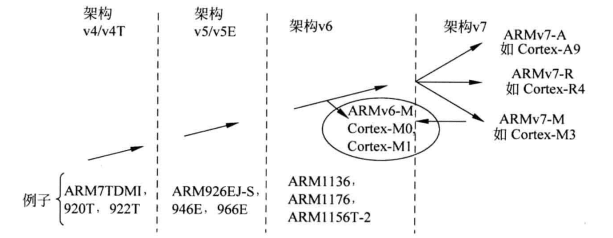

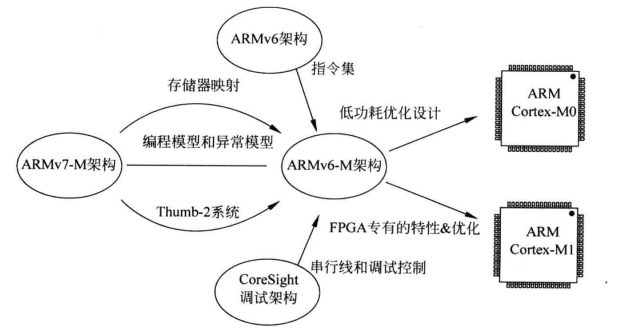

那么这些与 Cortex-M0 有什么关联呢?在 Cortex-M3 成功发布以后,ARM 决定拓展微控制器领域的应用。第一步让用户能够在可编程门阵列(FPGA)上很容易的使用 ARM 处理器,第二步的重点是超低功耗的嵌入式处理器应用。为了实现这一目标,ARM 在 ARMv7-M 架构的异常处理和调试特性的基础上,开发出一种全新的架构,并且使用现有的 ARMv6 架构的 Thumb 指令集。这样也就有了 ARMv6-M 架构,并在此基础上开发了 Cortex-M0 处理器(用于微控制器和专用IC)和 Cortex-M1 处理器(用于FPGA)。

ARM 处理器架构发展历程,如下图:

ARMv6 架构的处理器面积小、高效、易于使用、并且具有较高的性能。和 Cortex-M3 类似,Cortex-M0 和 Cortex-M1 包含了嵌套向量中断控制器(NVIC),使用相同的异常/中断处理机制;并且系统同 ARMv7-M 相似,也定义了线程模式(Thread mode)和异常模式(Exception mode)。

ARMv6-M 架构特性,如下图:

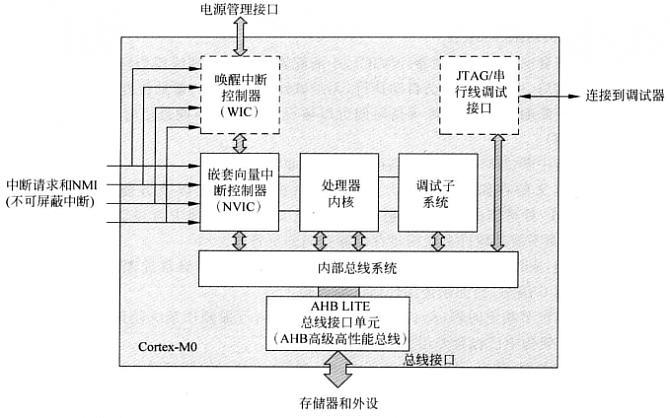

3. 处理器框图

Cortex-M0 总共支持56个基本指令。从理论上来说,由于读写存储器的指令相互独立,而且算术或逻辑操作的指令使用寄存器,Cortex-M0处理器可以被归于加载-存储(load-store)结构中。

处理器内核,包括:寄存器组、算术逻辑单元(ALU)、数据总线**** **和 **控制逻辑。流水线设计可以分为3种状态:取值、译码和执行。寄存器组包含16个32位寄存器,其中一些寄存器具有特殊的用途。

嵌入式向量中断控制器(NVIC),可以处理最多32个中断请求和一个不可屏蔽中断(NMI)输入。NVIC需要比较正在执行中断的优先级,然后自动执行高优先级中断。如果要处理一个中断,NVIC会和处理器进行通信,通知处理器执行正确的中断处理。

唤醒中断控制器(WIC),可选单元,在低功耗应用中,在关闭处理器大部分模块后,微控制器会进入待机模式。此时,WIC可以在NVIC和处理器处于休眠情况下,执行中断屏蔽功能。当WIC检测到一个中断时,会通知电源管理部分给系统上电,让NVIC和处理器内个执行剩下的中断处理。

调试子系统,包含多个功能模块,以及处理调试控制、程序断点和数据监视点。当调试事件发生时,处理器内核会暂停状态,这时开发人员可以检查当前处理器状态。

4. 处理器特性

4.1 系统特性

- Thumb指令集,兼具高效和高代码密度;

- 高性能,使用快速乘法器可以达到0.9DMIPS/MHz,较小的乘法器达到0.85DMIPS/Mhz;

- 内置嵌套向量中断控制器(NVIC),当接收到中断请求后,中断处理自动执行,无需软件查找中断向量位置;

- 确定的中断响应时间,中断等待时间可以被设定为固定值或最短时间(最小16个时钟周期);

- 不可屏蔽中断(NMI)输入;

- 内置系统节拍定时器(SysTick),24位定时器,可被操作系统使用。

- 请求管理调用,具有SVC异常和PendSVC异常,支持嵌入式OS的多种操作;

- 架构定义的休眠模式和进入休眠指令,能够使能量消耗极大降低;

- 异常处理可以捕获到系统中的多种错误;

4.2 应用特性

- 中断数量可配置(1~32个)

- 快速乘法器(单周期)和小型乘法器(较小硅片面积,低功耗,32周期)可供选择;

- 支持大端或小端存储器;

- 可选择的唤醒中断控制器(WIC)

4.3 调试特性

- 停止模式调试,处理器可以完全停止,此时寄存器可以被访问和修改;

- CoreSight技术,调试器可以在没有停止处理器情况下,操作存储器和外设’;

- 支持JTAG和SWD调试接口;

- 可配置数量的硬件断点(0~4个)和监视点(0~2个);

- 断点指令支持不限数量的软件断点;

5. 处理器优势

Cortex-M0的一个重要目标是降低功耗,使用65nm半导体工艺,处理器仅消耗12uW/MHz,180nm工艺则消耗85uW/MHz。对于32位处理器来说,已经是很低功耗了。

为了确保Cortex-M0实现低功耗目的,ARM做了以下几个方面的优化:

- 门数量低。 最低配置仅需12000门。为了性能更佳,门数的典型值在17000~25000。

- 高效率 Thumb指令集的效率和高度优化的硬件设计。

- 低功耗特性(休眠模式) 提供两个休眠模式,WFI(中断触发唤醒)和WFE(事件触发唤醒);初次之外,还包含了一个独一无二的功能,即唤醒中断控制器(WIC),利用这部分功能,即便处理器处于休眠状态,中断也可以将其立即唤醒,大大降低休眠时系统的漏电流(静态功耗)。

- 逻辑单元提升 除了降低晶体管的尺寸,ARM公司的 Physical IP 部门一直致力于降低嵌入式系统功耗的研究,他们的一个主要成果就是超低漏电流(ULL)逻辑单元库。