# RealView<sup>®</sup> Compilation Tools

Version 4.0

**Developer Guide**

Copyright © 2002-2010 ARM. All rights reserved. ARM DUI 0203J (ID101213)

## RealView Compilation Tools Developer Guide

Copyright © 2002-2010 ARM. All rights reserved.

#### **Release Information**

The following changes have been made to this book.

**Change History**

| Date             | Issue | Confidentiality  | Change                                           |

|------------------|-------|------------------|--------------------------------------------------|

| August 2002      | А     | Non-Confidential | Release 1.2                                      |

| January 2003     | В     | Non-Confidential | Release 2.0                                      |

| September 2003   | С     | Non-Confidential | Release 2.0.1 for ARM® RealView® Developer Suite |

| January 2004     | D     | Non-Confidential | Release 2.1 for RealView Developer Suite         |

| December 2004    | Е     | Non-Confidential | Release 2.2 for RealView Developer Suite         |

| May 2005         | F     | Non-Confidential | Release 2.2 SP1 for RealView Developer Suite     |

| March 2006       | G     | Non-Confidential | Release 3.0 for RealView Development Suite       |

| March 2007       | Н     | Non-Confidential | Release 3.1 for RealView Development Suite       |

| September 2008   | Ι     | Non-Confidential | Release 4.0 for RealView Development Suite       |

| 23 January 2009  | Ι     | Non-Confidential | Update 1 for RealView Development Suite v4.0     |

| 10 December 2010 | J     | Non-Confidential | Update 2 for RealView Development Suite v4.0     |

#### **Proprietary Notice**

Words and logos marked with <sup>®</sup> or <sup>™</sup> are registered trademarks or trademarks of ARM<sup>®</sup> in the EU and other countries, except as otherwise stated below in this proprietary notice. Other brands and names mentioned herein may be the trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM in good faith. However, all warranties implied or expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product.

Where the term ARM is used it means "ARM or any of its subsidiaries as appropriate".

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

Unrestricted Access is an ARM internal classification.

#### **Product Status**

The information in this document is final, that is for a developed product.

#### Web Address

http://www.arm.com

## Contents RealView Compilation Tools Developer Guide

|           | Prefa | ace                                 |      |

|-----------|-------|-------------------------------------|------|

|           |       | About this book                     |      |

|           |       | Feedback                            | xii  |

| Chapter 1 | Intro | duction                             |      |

| -         | 1.1   | About RealView Compilation Tools    | 1-2  |

|           | 1.2   | Using the examples                  |      |

| Chapter 2 | Deve  | eloping for ARM Processors          |      |

|           | 2.1   | About the ARM architectures         | 2-2  |

|           | 2.2   | ARM architecture v4T                | 2-8  |

|           | 2.3   | ARM architecture v5TE               | 2-10 |

|           | 2.4   | ARM architecture v6                 | 2-12 |

|           | 2.5   | ARM architecture v6-M               | 2-16 |

|           | 2.6   | ARM architecture v7-A               | 2-18 |

|           | 2.7   | ARM architecture v7-R               | 2-20 |

|           | 2.8   | ARM architecture v7-M               | 2-22 |

| Chapter 3 | Emb   | edded Software Development          |      |

| •         | 3.1   | About embedded software development | 3-2  |

|           | 3.2 Default compilation tool behavior                           | 3-4  |

|-----------|-----------------------------------------------------------------|------|

|           | 3.3 Tailoring the C library to your target hardware             | 3-9  |

|           | 3.4 Tailoring the image memory map to your target hardware      | 3-11 |

|           | 3.5 Reset and initialization                                    | 3-16 |

|           | 3.6 Target hardware and the memory map                          | 3-22 |

| Chapter 4 | Mixing C, C++, and Assembly Language                            |      |

| -         | 4.1 Using instruction intrinsics, inline and embedded assembler | 4-2  |

|           | 4.2 Accessing C global variables from assembly code             | 4-4  |

|           | 4.3 Using C header files from C++                               | 4-5  |

|           | 4.4 Calling between C, C++, and ARM assembly language           | 4-7  |

| Chapter 5 | Interworking ARM and Thumb                                      |      |

| •         | 5.1 About interworking                                          | 5-2  |

|           | 5.2 Assembly language interworking                              |      |

|           | 5.3 C and C++ interworking                                      |      |

|           | 5.4 Interworking examples                                       | 5-7  |

| Chapter 6 | Handling Processor Exceptions                                   |      |

| -         | 6.1 About processor exceptions                                  | 6-2  |

|           | 6.2 ARMv6 and earlier, ARMv7-A and ARMv7-R profiles             | 6-3  |

|           | 6.3 ARMv6-M and ARMv7-M profiles                                |      |

| Chapter 7 | Debug Communications Channel                                    |      |

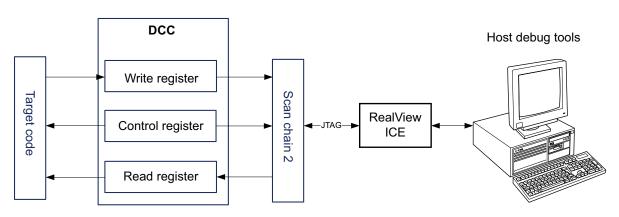

| •         | 7.1 About the Debug Communications Channel                      | 7-2  |

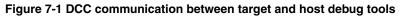

|           | 7.2 DCC communication between target and host debug tools       |      |

|           | 7.3 Access from Thumb state                                     | 7-6  |

| Chapter 8 | Semihosting                                                     |      |

| •         | 8.1 About semihosting                                           | 8-2  |

|           | 8.2 Semihosting implementation                                  |      |

|           | 8.3 Semihosting operations                                      |      |

|           | 8.4 Debug agent interaction SVCs                                |      |

## Preface

This preface introduces the ARM<sup>®</sup> *RealView<sup>®</sup> Compilation Tools Developer Guide*. It contains the following sections:

- About this book on page viii

- *Feedback* on page xii.

## About this book

This book contains information that helps you to develop code for the ARM family of processors. The chapters in this book, and the examples used, assume that you are using the latest release of the ARM RealView Compilation Tools to develop your code.

## Intended audience

This book is written for all developers who are producing applications using RealView Compilation Tools. It assumes that you are an experienced software developer, and that you are familiar with the ARM tools described in the *RealView Compilation Tools Essentials Guide*.

## Using this book

This book is organized into the following chapters:

### **Chapter 1** Introduction

Read this chapter for an introduction to RealView Compilation Tools.

### Chapter 2 Developing for ARM Processors

Read this chapter for information on the key features for each type of architecture and to identify some of the main points to be aware of when using the RealView Compilation Tools.

## Chapter 3 Embedded Software Development

Read this chapter for information about how to develop embedded applications with RealView Compilation Tools. It describes the default RealView Compilation Tools behavior in the absence of a target system, and how to tailor the C library and image memory map to your target system.

## Chapter 5 Interworking ARM and Thumb

Read this chapter for information about how to change between ARM state and Thumb<sup>®</sup> state when writing code for processors that implement the Thumb instruction set.

## Chapter 4 Mixing C, C++, and Assembly Language

Read this chapter for information about how to write a mixture of C, C++, and ARM assembly language code for the ARM architecture. It also describes how to use the ARM instruction intrinsics, inline assembler, and embedded assembler in C and C++ files.

## **Chapter 6** Handling Processor Exceptions

Read this chapter for information about how to handle the various types of exception supported by ARM processors.

## **Chapter 7** Debug Communications Channel

Read this chapter for a description of how to use the *Debug Communications Channel* (DCC).

## **Chapter 8** Semihosting

Read this chapter for information about the semihosting mechanism. Semihosting enables code running on an ARM target to use the I/O facilities on a host computer that is running an ARM debugger.

This book assumes that the ARM software is installed in the default location. For example, on Windows this might be *volume*:\Program Files\ARM. This is assumed to be the location of *install\_directory* when referring to path names. For example *install\_directory*\Documentation\.... You might have to change this if you have installed your ARM software in a different location.

## **Typographical conventions**

The following typographical conventions are used in this book:

| monospace         | Denotes text that can be entered at the keyboard, such as commands, file<br>and program names, and source code.                                              |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>mono</u> space | Denotes a permitted abbreviation for a command or option. The<br>underlined text can be entered instead of the full command or option<br>name.               |

| monospace i       | talic                                                                                                                                                        |

|                   | Denotes arguments to commands and functions where the argument is to be replaced by a specific value.                                                        |

| monospace b       | old                                                                                                                                                          |

|                   | Denotes language keywords when used outside example code.                                                                                                    |

| italic            | Highlights important notes, introduces special terminology, denotes internal cross-references, and citations.                                                |

| bold              | Highlights interface elements, such as menu names. Also used for<br>emphasis in descriptive lists, where appropriate, and for ARM processor<br>signal names. |

## **Further reading**

This section lists publications from both ARM and third parties that provide additional information on developing code for the ARM family of processors.

ARM periodically provides updates and corrections to its documentation. See http://infocenter.arm.com/help/index.jsp for current errata sheets and addenda, and the ARM *Frequently Asked Questions* (FAQs).

## **ARM** publications

This book contains general information on developing applications for the ARM family of processors. Other publications included in the suite are:

- *RVCT Essentials Guide* (ARM DUI 0202)

- *RVCT Compiler User Guide* (ARM DUI 0205)

- *RVCT Compiler Reference Guide* (ARM DUI 0348)

- RVCT Libraries and Floating Point Support Guide (ARM DUI 0349)

- *RVCT Linker User Guide* (ARM DUI 0206)

- *RVCT Linker Reference Guide* (ARM DUI 0381)

- *RVCT Utilities Guide* (ARM DUI 0382)

- *RVCT Assembler Guide* (ARM DUI 0204).

For full information about the base standard, software interfaces, and standards supported by ARM, see *install\_directory*\Documentation\Specifications\....

In addition, see the following documentation for specific information relating to ARM products:

- *ARM Architecture Reference Manual, ARMv7-A and ARMv7-R edition* (ARM DDI 0406)

- ARMv7-M Architecture Reference Manual (ARM DDI 0403)

- ARMv6-M Architecture Reference Manual (ARM DDI 0419)

- ARM Architecture Reference Manual (ARM DDI 0100)

- ARM datasheet or technical reference manual for your hardware device.

## Other publications

For an introduction to ARM architecture, see Andrew N. Sloss, Dominic Symes and Chris Wright, *ARM System Developer's Guide: Designing and Optimizing System Software* (2004). Morgan Kaufmann, ISBN 1-558-60874-5.

For an essential handbook for system-on-chip designers using ARM processors and engineers working with the ARM architecture, see Steve Furber, *ARM system-on-chip architecture* (2nd edition, 2000). Addison Wesley, ISBN 0-201-67519-6.

## Feedback

ARM welcomes feedback on both RealView Compilation Tools, and its documentation.

## Feedback on RealView Compilation Tools

If you have any problems with RealView Compilation Tools, contact your supplier. To help them provide a rapid and useful response, give:

- your name and company

- the serial number of the product

- details of the release you are using

- details of the platform you are running on, such as the hardware platform, operating system type and version

- a small standalone sample of code that reproduces the problem

- a clear explanation of what you expected to happen, and what actually happened

- the commands you used, including any command-line options

- sample output illustrating the problem

- the version string of the tool, including the version number and date.

## Feedback on this book

If you notice any errors or omissions in this book, send email to errata@arm.com giving:

- the document title

- the document number

- the page numbers to which your comments apply

- a concise explanation of the problem.

General suggestions for additions and improvements are also welcome.

## Chapter 1 Introduction

This chapter introduces the ARM  $^{\mbox{\tiny @}}$  RealView  $^{\mbox{\tiny @}}$  Compilation Tools.

It contains the following sections:

- About RealView Compilation Tools on page 1-2

- Using the examples on page 1-3.

## 1.1 About RealView Compilation Tools

RealView Compilation Tools consists of a suite of applications, together with supporting documentation and examples, that enable you to write applications for the ARM family of processors. You can use RealView Compilation Tools to build C, C++, and ARM assembly language programs.

This book contains information that helps you to develop code for ARM processors. The chapters in this book, and the examples used, assume that you are using the latest release of RealView Compilation Tools to develop your code.

If you are upgrading to RealView Compilation Tools from a previous release, ensure that you read the *RealView Compilation Tools Essentials Guide* for information about new features and enhancements in this release.

If you are new to RealView Compilation Tools, read the *RealView Compilation Tools Essentials Guide* for an overview of the ARM tools and an introduction to using them as part of your development project.

For information about previous releases of RealView Compilation Tools, see Appendix A in the *RealView Compilation Tools Essentials Guide*.

See *ARM publications* on page x for a list of the other books in the RealView Compilation Tools documentation suite that give information on the ARM assembler, ARM compiler, ARM linker, and supporting software.

## 1.2 Using the examples

This book uses the examples provided with RealView Development Suite. These can be found in the examples directory *install\_directory*\RVDS\Examples. See the *RealView Development Suite Getting Started Guide* for a summary of the examples provided.

Introduction

## Chapter 2 Developing for ARM Processors

This chapter describes the key features for each version of the architecture and identifies some of the main points to be aware of when using the ARM RealView Compilation Tools.

It contains the following sections:

- *About the ARM architectures* on page 2-2

- ARM architecture v4T on page 2-8

- *ARM architecture v5TE* on page 2-10

- *ARM architecture v6* on page 2-12

- ARM architecture v6-M on page 2-16

- ARM architecture v7-A on page 2-18

- *ARM architecture v7-R* on page 2-20

- *ARM architecture v7-M* on page 2-22.

## 2.1 About the ARM architectures

This section gives an overview of the various ARM architectures and associated features to be aware of when developing code for specific processors.

ARM architectures provide support for the 32-bit ARM and 16-bit Thumb<sup>®</sup> instruction set architectures along with architecture extensions to provide support for *Tightly Coupled Memory* (TCM), memory management, *Single Instruction Multiple Data* (SIMD), and NEON<sup>™</sup> technologies.

The ARM architecture is constantly improving to meet the increasing demands of leading edge applications developers, while retaining the backwards compatibility necessary to protect investment in software development.

For more information, see the *Technical Reference Manual* for your processor or the *ARM Architecture Reference Manual*.

Table 2-1 gives an overview of some key features for the ARM processors.

| Table 2-1 | Key | features |

|-----------|-----|----------|

|-----------|-----|----------|

| Processor                                           | Architecture | Tightly<br>Coupled<br>Memory | Memory<br>Management | Thumb-2 |

|-----------------------------------------------------|--------------|------------------------------|----------------------|---------|

| ARM7TDMI®                                           | ARMv4T       | -                            | -                    | -       |

| ARM920T <sup>™</sup>                                | ARMv4T       | -                            | MMU                  | -       |

| ARM922T <sup>™</sup>                                | ARMv4T       | -                            | MMU                  | -       |

| ARM926EJ-S™                                         | ARMv5TEJ     | Yes                          | MMU                  | -       |

| ARM946E-S <sup>™</sup>                              | ARMv5TE      | Yes                          | MPU                  | -       |

| ARM966E-S <sup>™</sup>                              | ARMv5TE      | Yes                          | -                    | -       |

| ARM11 <sup>™</sup> MPCore <sup>™</sup>              | ARMv6K       | -                            | MMU                  | -       |

| ARM1136J-S <sup>™</sup> /ARM1136JF-S <sup>™</sup>   | ARMv6K       | Yes                          | MMU                  | -       |

| ARM1156T2-S <sup>™</sup> /ARM1156T2F-S <sup>™</sup> | ARMv6T2      | Yes                          | MPU                  | Yes     |

| ARM1176JZ-S <sup>™</sup> /ARM1176JZF-S <sup>™</sup> | ARMv6Z       | Yes                          | MMU                  | -       |

| ARM11 <sup>™</sup> MPCore <sup>™</sup>              | ARMv6K       | -                            | MMU                  | -       |

| Cortex <sup>™</sup> -M0                             | ARMv6-M      | -                            | -                    | -       |

| Cortex <sup>™</sup> -M1                             | ARMv6-M      | Yes                          | -                    | -       |

| Processor                | Architecture | Tightly<br>Coupled<br>Memory | Memory<br>Management | Thumb-2      |

|--------------------------|--------------|------------------------------|----------------------|--------------|

| Cortex-M3                | ARMv7-M      | -                            | MPU (optional)       | Thumb-2 only |

| Cortex-M4                | ARMv7E-M     | -                            | MPU (optional)       | Thumb-2 only |

| Cortex-A5                | ARMv7-A      | -                            | MMU                  | Yes          |

| Cortex-A8                | ARMv7-A      | -                            | MMU                  | Yes          |

| Cortex-A9                | ARMv7-A      | -                            | MMU                  | Yes          |

| Cortex-R4 and Cortex-R4F | ARMv7-R      | Variable                     | MPU                  | Yes          |

## Table 2-1 Key features (continued)

## 2.1.1 Multiprocessing systems

The ARM architecture v6K introduces the first MPCore processor supporting up to four CPUs and associated hardware. Applications have to be specifically designed to run on multiprocessing systems to optimize performance. For example, a CPU can be dedicated to a particular task in a single threaded application or used for parallel processing in a multi threaded environment. An efficient multiprocessing system consumes less power, produces less heat and is more responsive than a system with one CPU but is more complex and therefore more difficult to debug.

Some points for consideration when designing a multiprocessing system:

- synchronize using LDREX/STREX to create a mutex or semaphore to protect critical sections and non-shareable resources

- enforce cache coherency for symmetrical multiprocessing

- execute repetitive tasks in separate threads

- split a large task into several threads executing in parallel

- set up a primary CPU using the CP15 CPU ID register for initialization tasks

- prioritize interrupts

- use bit masking for interrupt pre-emption

- configure the cycle counts that trigger a timer or watchdog.

\_\_\_\_\_Note \_\_\_\_\_

These tasks are generally handled by an OS.

## 2.1.2 Tightly coupled memory

TCM is a contiguous area of memory that is always valid if the TCM is enabled. TCM is used as part of the physical memory map of the system, and does not have to be backed by a level of external memory with the same physical addresses. For this reason, the TCM behaves differently from the caches for regions of memory that are marked as being write-through cacheable. In such regions, no external writes occur in the event of a write to memory locations contained in the TCM.

The purpose of TCM is to provide low-latency memory that the processor can use without the unpredictability that is a feature of caches. You can use TCM to hold critical routines, such as interrupt handling routines or real-time tasks where the indeterminacy of a cache is highly undesirable. In addition, you can use it to hold scratch pad data, data types whose locality properties are not well suited to caching, and critical data structures such as interrupt stacks.

For a full architectural description of a TCM, see the *ARM Architecture Reference Manual* and the *Technical Reference Manual* for your processor.

## 2.1.3 Memory management

The ARM memory management options are:

- **MMU** The *Memory Management Unit* (MMU) allows fine-grained control of a memory system. Most of the detailed control is provided through translation tables held in memory. Entries in these tables define the properties for different regions of memory. These include:

- virtual-to-physical address mapping

- memory access permissions

- memory types.

- MPU The *Memory Protection Unit* (MPU) provides a considerably simpler alternative to the MMU. This allows both hardware and software to be simplified in systems that do not require all facilities of the MMU. You can use the MPU to partition external memory into separate contiguous regions with different sizes and attributes. You can also control access permissions and memory characteristics for different regions of memory.

An MPU does not require external memory for translation tables and it must be enabled before the caches can be enabled.

For a full architectural description of an MMU or MPU, see the *ARM Architecture Reference Manual* and the *Technical Reference Manual* for your processor.

## 2.1.4 Thumb-2

Thumb-2 technology is available in the ARMv6T2 and later architectures. Thumb-2 is a major enhancement to the 16-bit Thumb instruction set. It adds 32-bit instructions that can be freely intermixed with 16-bit instructions in a program. The additional 32-bit instructions enable Thumb-2 to cover the functionality of the ARM instruction set. The 32-bit instructions enable Thumb-2 to combine the code density of earlier versions of Thumb, with performance of the ARM instruction set.

The most important difference between the Thumb-2 instruction set and the ARM instruction set is that most 32-bit Thumb instructions are unconditional, whereas most ARM instructions can be conditional. Thumb-2 introduces a conditional execution instruction, IT, that is a logical if-then-else operation that you can apply to subsequent instructions to make them conditional.

For more information on the instruction set, see the *ARM Architecture Reference Manual* and the *Technical Reference Manual* for your processor.

## 2.1.5 Floating-point build options

The following guidelines can be used to help you select the most suitable floating-point build options to use for your application.

## ARM and Thumb floating-point (ARMv6 and earlier)

There are several options for compiling code that carries out floating-point operations in ARM state code and Thumb state code:

**ARM only** Choose the option --fpu vfpv2 to have the compiler generate ARM code only for functions containing floating-point operations.

When the option -- fpu vfpv2 is selected, the compiler generates ARM code for any function containing floating-point operations, regardless of whether the compiler is compiling for ARM or compiling for Thumb.

Functions containing floating-point operations and that are compiled for Thumb are compiled to ARM code, because Thumb code cannot contain VFP instructions or access VFP registers. This uses hardware VFP linkage. When compiling for ARM only, use --fpu=vfp and not --fpu=softvfp+vfp. Software linkage adds an overhead in transfer values between VFP and ARM that slows down the transfers and requires additional instructions.

## Mixed ARM/Thumb

Choose the option -- fpu softvfp+vfpv2 to have the compiler generate mixed ARM/Thumb code.

When the option --fpu softvfp+vfpv2 is selected, all functions are compiled using software floating-point linkage. This means that floating-point arguments are passed to and returned from functions in integer registers.

The Thumb instruction set does not contain VFP instructions and therefore cannot access VFP registers. Therefore, for Thumb code, when --fpu=softvfp+vfpv2 is used, the compiler generates calls to library functions to perform the VFP operations. These library functions have to use software linkage because the Thumb code cannot access the VFP registers that are required to use hardware linkage.

The RVCT libraries include versions of the software floating point functions that are compiled for ARM, and use VFP instructions to be used with --fpu=softvfp+vfpv2. These library functions give improved performance and reduced code size compared to the full software floating point functions.

The option that provides the best code size or performance depends on the code being compiled. When compiling for ARM, it is best to experiment with the options --fpu softvfp+vfpv2 and --fpu vfpv2 to determine which provides the required code size and performance attributes.

If you have a mix of ARM and Thumb then you might want to experiment with the -- fpu option to get the best results.

## ARM and Thumb-2 floating-point (ARMv7, RealView Development Suite v3.0 and later)

## Mixed ARM/Thumb-2

Choose the option -- fpu softvfp+vfpv3 to have the compiler generate mixed ARM/Thumb code.

When the option --fpu softvfp+vfpv3 is selected, all functions are compiled using software floating-point linkage. This means that floating-point arguments are passed to and returned from functions in ARM integer registers. Software floating-point linkage enables you to link with generic libraries and legacy code that are themselves built with software floating-point linkage.

**ARM only** Choose the options --arm --fpu vfpv3 to have the compiler generate ARM code only. This uses hardware VFP linkage.

## Thumb-2 only

Choose the options --thumb --fpu vfpv3 to have the compiler generate Thumb-2 code only for your entire program. Thumb-2 supports VFP instructions. Therefore, there is no need to switch to ARM state to perform VFP operations. This uses hardware VFP linkage.

## – Note –––––

This option is available only for ARMv7 processors with VFPv3, for example the Cortex-A8, where VFP is directly accessible from both the ARM and Thumb-2 instruction set.

## 2.2 ARM architecture v4T

This section gives an overview of the RealView tools support for ARMv4T. This variant of the ARM architecture provides 16-bit Thumb instructions, a subset of the 32-bit ARM instruction set. It supports both ARM and Thumb instruction sets.

#### Table 2-2 Useful command-line options

| Command-line option | Description                                                                                                                      |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------|

| cpu=4T              | ARMv4 with Thumb.                                                                                                                |

| cpu=name            | Where <i>name</i> is a specific ARM processor. For example ARM7TDMI.                                                             |

| apcs=qualifier      | Where <i>qualifier</i> denotes one or more qualifiers for interworking and position independence.<br>For exampleapcs=/interwork. |

## 2.2.1 Key features

When compiling code for ARMv4T, the compiler supports the additional Thumb instructions for greater code density but with the following limitations:

- Thumb code usually uses more instructions for a given task, making ARM code best for maximizing performance of time-critical code

- ARM state and associated ARM instructions are required for exception handling.

## 2.2.2 Alignment support

All load and store instructions must specify addresses that are aligned on a natural alignment boundary. For example:

- LDR and STR addresses must be aligned on a word boundary

- LDRH and STRH addresses must be aligned on a halfword boundary

- LDRB and STRB addresses can be aligned to any boundary.

Accesses to addresses that are not on a natural alignment boundary result in unpredictable behavior. To control this you must inform the compiler, using \_\_packed, when you want to access an unaligned address so that it can generate safe code. See \_\_packed on page 4-11 in the *Compiler Reference Guide*.

—— Note ———

Unaligned accesses, where permitted, are treated as rotated aligned accesses.

## 2.2.3 Endian support

You can produce either little-endian or big-endian code using the compiler command-line options --littleend and --bigend respectively.

ARMv4T supports the following endian modes:

- LE little-endian format

- **BE-32** legacy big-endian format.

## 2.3 ARM architecture v5TE

This section gives an overview of the RealView tools support for ARMv5TE. This variant of the ARM architecture provides enhanced arithmetic support for *Digital Signal Processing* (DSP) algorithms. It supports both ARM and Thumb instruction sets.

#### Table 2-3 Useful command-line options

| Command-line option | Description                                                                                                                                                                     |  |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| cpu=5TE             | ARMv5 with Thumb, interworking, DSP multiply, and double-word instructions                                                                                                      |  |

| cpu=5TEJ            | ARMv5 with Thumb, interworking, DSP multiply, double-word instructions, and Jazelle® extensions <sup>a</sup>                                                                    |  |

| Cpu=name            | <ul> <li>Where <i>name</i> is a specific ARM processor. For example:</li> <li>ARM926EJ-S for ARMv5 with Thumb, Jazelle extensions, physically mapped caches and MMU.</li> </ul> |  |

a. The ARM compiler cannot generate Jazelle bytecodes.

## 2.3.1 Key features

When compiling code for ARMv5TE, the compiler:

- Supports improved interworking between ARM and Thumb, for example BLX.

- Performs instruction scheduling for the specified processor. Instructions are re-ordered to minimize interlocks and improve performance.

- Uses multiply and multiply-accumulate instructions that act on 16-bit data items.

- Uses instruction intrinsics to generate addition and subtraction instructions that perform saturated signed arithmetic. Saturated arithmetic produces the maximum positive or negative value instead of wrapping the result if the calculation overflows the normal integer range.

- Uses load (LDRD) and store (STRD) instructions that act on two words of data.

- Uses a preload data instruction PLD.

## 2.3.2 Alignment support

All load and store instructions must specify addresses that are aligned on a natural alignment boundary. For example:

- LDR and STR addresses must be aligned on a word boundary

- LDRH and STRH addresses must be aligned on a halfword boundary

- LDRD and STRD addresses must be aligned on a doubleword boundary

- LDRB and STRB addresses can be aligned to any boundary.

Accesses to addresses that are not on a natural alignment boundary result in unpredictable behavior. To control this you must inform the compiler, using \_\_packed, when you want to access an unaligned address so that it can generate safe code. See \_\_packed on page 4-11 in the *Compiler Reference Guide*.

All LDR and STR instructions, except LDRD and STRD, must specify addresses that are word-aligned, otherwise the instruction generates an abort.

\_\_\_\_ Note \_\_\_\_\_

Unaligned accesses, where permitted, are treated as rotated aligned accesses.

## See also

- Technical Reference Manual for your processor

- Aligning data on page 5-25 in the Compiler User Guide

- --unaligned\_access, --no\_unaligned\_access on page 2-128 in the Compiler Reference Guide.

## 2.3.3 Endian support

You can produce either little-endian or big-endian code using the compiler command-line options --littleend and --bigend respectively.

ARMv5TE supports the following endian modes:

**BE-32** legacy big-endian format.

## 2.4 ARM architecture v6

This section gives an overview of the RealView tools support for ARMv6. This variant of the ARM architecture extends the original ARM instruction set to support multi-processing and adds some extra memory model features. It supports both ARM and Thumb instruction sets.

#### Table 2-4 Useful command-line options

| Option   | Description                                                                                                                                                                                                                                  |  |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| cpu=6    | ARMv6 with Thumb, interworking, DSP multiply, doubleword instructions, unaligned and mixed-endian support, Jazelle, and media extensions                                                                                                     |  |

| cpu=6Z   | ARMv6 with security extensions                                                                                                                                                                                                               |  |

| cpu=6T2  | ARMv6 with Thumb-2                                                                                                                                                                                                                           |  |

| cpu=name | <ul> <li>Where <i>name</i> is a specific ARM processor. For example:</li> <li>ARM1136J-S to generate code for the ARM1136J-S with software VFP support</li> <li>ARM1136JF-S to generate code for the ARM1136J-S with hardware VFP</li> </ul> |  |

## 2.4.1 Key features

When compiling code for ARMv6, the compiler:

- Performs instruction scheduling for the specified processor. Instructions are re-ordered to minimize interlocks and improve performance.

- Generates explicit SXTB, SXTH, UXTB, UXTH byte or halfword extend instructions where appropriate.

- Generates the endian reversal instructions REV, REV16 and REVSH if it can deduce that a C expression performs an endian reversal.

- Generates additional Thumb instructions available in ARMv6, for example CPS, CPY, REV, REV16, REVSH, SETEND, SXTB, SXTH, UXTB, UXTH.

- Uses some functions that are optimized specifically for ARMv6, for example, memcpy().

The compiler cannot generate SIMD instructions, because these do not map well onto C expressions. You must use assembly language or intrinsics for SIMD code generation.

Some enhanced instructions are available to improve exception handling:

• SRS and RFE instructions to save and restore the *Link Register* (LR) and the *Saved Program Status Register* (SPSR)

- CPS simplifies changing state, and modifying the I and F bits in the *Current Program Status Register* (CPSR)

- architectural support for vectored interrupts with a vectored interrupt controller

- low-latency interrupt mode

- ARM1156T2-S can enter exceptions in Thumb state using Thumb-2 code.

## 2.4.2 Alignment support

By default, the compiler uses ARMv6 unaligned access support to speed up access to packed structures, by allowing LDR and STR instructions to load from and store to words that are not aligned on natural word boundaries. Structures remain unpacked unless explicitly qualified with \_\_packed. Table 2-5 shows the effect of one-byte alignment when compiling for ARMv6 and earlier architectures.

### Table 2-5 One-byte alignment

| <pre>packed struct {     int i;     char ch;     short sh; } foo;</pre>                                                                    |                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| Compiling for pre-ARMv6:<br>MOV R4,R0<br>BLaeabi_uread4<br>LDRB R1, [R4,#4]<br>LDRSB R2,[R4,#5]<br>LDRB R12,[R4,#6]<br>ORR R2,R12,R2 LSL#8 | Compiling for ARMv6 and later:<br>LDR R0, [R4,#0]<br>LDRB R1,[R4,#4]<br>LDRSH R2,[R4,#5] |

Code compiled for ARMv6 only runs correctly if you enable unaligned data access support on your processor. You can control alignment by using the U and the A bits in the CP15 register c1, or by typing the **UBITINIT** input to the processor HIGH.

Code that uses the behavior of pre-ARMv6 unaligned data accesses can be generated by using the compiler option --no\_unaligned\_access.

\_\_\_\_ Note \_\_\_\_\_

Unaligned data accesses are not available in BE-32 endian mode.

LDRD and STRD might be word aligned.

## See also

Technical Reference Manual for your processor

- Aligning data on page 5-25 in the Compiler User Guide

- --unaligned\_access, --no\_unaligned\_access on page 2-128 in the Compiler Reference Guide.

## 2.4.3 Endian support

You can produce either little-endian or big-endian code using the compiler command-line options --littleend and --bigend respectively.

ARMv6 supports the following endian modes:

| LE    | little-endian format      |

|-------|---------------------------|

| BE8   | big-endian format         |

| BE-32 | legacy big-endian format. |

Mixed endian systems are also possible by using SETEND and REV instructions.

## Compiling for ARMv6 endian mode BE8

By default, the compiler generates BE8 big-endian code when compiling for ARMv6 and big-endian. The compiler sets a flag in the code that labels the code as BE8. Therefore, to enable BE8 support in the ARM processor you normally have to set the E-bit in the CPSR.

It is possible to link legacy code with ARMv6 code for running on an ARMv6 based processor. However, in this case the linker switches the byte order of the legacy code into BE8 mode. The resulting image is in BE8 mode.

## Compiling for ARMv6 legacy endian mode BE32

To use the pre-ARMv6 or legacy BE32 mode you must tie the BIGENDINIT input into the processor HIGH, or set the B bit of CP15 register c1.

\_\_\_\_\_Note \_\_\_\_\_

You must link BE32-compatible code using the linker option --be32. Otherwise, the ARMv6 attributes causes a BE8 image to be produced.

For more information see:

- Alignment support on page 2-13

- --bigend on page 2-17 in the Compiler Reference Guide

- --littleend on page 2-85 in the Compiler Reference Guide

- --unaligned\_access, --no\_unaligned\_access on page 2-128 in the Compiler Reference Guide

- -- *be8* on page 2-15 in the *Linker Reference Guide*

- --*be32* on page 2-16 in the *Linker Reference Guide*.

## 2.5 ARM architecture v6-M

This section gives an overview of the RealView tools support for ARMv6-M. Microcontroller profiles implement a programmers' model designed for fast interrupt processing, with hardware stacking of registers and support for writing interrupt handlers in high-level languages. It is intended for deeply embedded applications that require a small processor integrated into an FPGA and supports the Thumb instruction set and a small number of 32-bit Thumb-2 instructions.

#### Table 2-6 Useful command-line options

| Command-line option | Description                                                                                                                                                                                                            |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| cpu=6-M             | ARMv6 microcontroller profile with Thumb only, and processor state instructions                                                                                                                                        |

| cpu=6S-M            | ARMv6 microcontroller profile with Thumb only, plus processor state instructions and OS extensions                                                                                                                     |

| cpu=name            | <ul> <li>Where <i>name</i> is a specific ARM processor. For example:</li> <li>Cortex-M1 for ARMv6 with Thumb only, plus processor state instructions, OS extensions and BE8 and LE data endianness support.</li> </ul> |

## 2.5.1 Key features

Key features for ARMv6-M:

• The compiler supports the extension of the Thumb instruction set using Thumb-2 technology. For example, BL, DMB, DSB, ISB, MRS and MSR.

## 2.5.2 Alignment support

By default, the compiler uses ARMv6 unaligned access support to speed up access to packed structures, by allowing LDR and STR instructions to load from and store to words that are not aligned on natural word boundaries.

Unaligned data accesses are converted into two or three aligned accesses, depending on the size and alignment of the unaligned access. This stalls any subsequent accesses until the unaligned access has completed. You can control alignment by using the DCode and System bus interfaces.

## See also

- Cortex-M1 Technical Reference Manual

- Cortex-M0 Technical Reference Manual

- Aligning data on page 5-25 in the Compiler User Guide

• --*unaligned\_access, --no\_unaligned\_access* on page 2-128 in the *Compiler Reference Guide*.

## 2.5.3 Endian support

You can produce either little-endian or big-endian code using the compiler command-line options --littleend and --bigend respectively.

ARMv6-M supports the following endian modes:

| LE | little-endian format |

|----|----------------------|

|    |                      |

**BE8** big-endian format.

## 2.6 ARM architecture v7-A

This section gives an overview of the RealView tools support for ARMv7-A. Application profiles implement a traditional ARM architecture with multiple modes and support a virtual memory system architecture based on an MMU. These profiles support both ARM and Thumb instruction sets.

#### Table 2-7 Useful command-line options

| Command-line option | Description                                                                                                                                                                                 |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| cpu=7               | ARMv7 with Thumb-2 only, and without hardware divide <sup>a</sup>                                                                                                                           |

| cpu=7-A             | ARMv7 application profile supporting virtual MMU-based memory systems, with ARM, Thumb, Thumb-2, and Thumb-2EE instruction sets, NEON <sup>™</sup> support, and 32-bit SIMD support         |

| cpu=name            | <ul> <li>Where <i>name</i> is a specific ARM processor. For example:</li> <li>Cortex-A8 for ARMv7 with ARM, Thumb, Thumb-2, hardware VFP, NEON support, and 32-bit SIMD support.</li> </ul> |

a. ARM v7 is not a recognized ARM architecture. Rather, it denotes the features that are common to all of the ARMv7-A, ARMv7-R, and ARMv7-M architectures.

### 2.6.1 Key features

Key features for ARMv7-A:

- Supports the advanced SIMD extensions

- Supports the *Thumb Execution Environment* (ThumbEE).

## 2.6.2 Alignment support

The data alignment behavior supported by the ARM architecture is significantly different between ARMv4 and ARMv7. An ARMv7 implementation must support unaligned data accesses. You can control the alignment requirements of load and store instructions by using the A bit in the CP15 register c1.

—— Note ——

ARMv7 architectures do not support pre-ARMv6 alignment.

#### See also

- Technical Reference Manual for your processor

- Aligning data on page 5-25 in the Compiler User Guide

• --unaligned\_access, --no\_unaligned\_access on page 2-128 in the Compiler Reference Guide.

## 2.6.3 Endian support

You can produce either little-endian or big-endian code using the compiler command-line options --littleend and --bigend respectively.

ARMv7-A supports the following endian modes:

**BE8** big-endian format used by ARMv6 and ARMv7.

The ARMv7 does not support the legacy BE-32 mode. If you have legacy code for ARMv7 processors that contain instructions with a big-endian byte order, then you must perform byte order reversal. See the *ARM Architecture Reference Manual*.

## 2.7 ARM architecture v7-R

This section gives an overview of the RealView tools support for ARMv7-R. Real-time profiles implement a traditional ARM architecture with multiple modes and support a protected memory system architecture based on an MPU. The ARMv7-R architecture supports both ARM and Thumb instruction sets.

### Table 2-8 Useful command-line options

| Command-line option | Description                                                                                                                                                                             |  |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| cpu=7               | ARMv7 with Thumb-2 only but without hardware divide <sup>a</sup>                                                                                                                        |  |

| cpu=7-R             | ARMv7 real-time profile with ARM, Thumb, Thumb-2 optional, VFP, 32-bit SIMD support, and hardware divide                                                                                |  |

| cpu=name            | <ul> <li>Where <i>name</i> is a specific ARM processor. For example:</li> <li>Cortex-R4F for ARMv7 with ARM, Thumb, Thumb-2, hardware VFP, hardware divide and SIMD support.</li> </ul> |  |

a. ARM v7 is not a recognized ARM architecture. Rather, it denotes the features that are common to all of the ARMv7-A, ARMv7-R, and ARMv7-M architectures.

## 2.7.1 Key features

Key features for ARMv7-R:

• Supports the SDIV and UDIV instructions.

## 2.7.2 Alignment support

The data alignment behavior supported by the ARM architecture has changed significantly between ARMv4 and ARMv7. An ARMv7 implementation provides hardware support for some unaligned data accesses using LDR, STR, LDRH, and STRH. Other data accesses must maintain alignment using LDM, STM, LDRD, STRD, LDC, STC, LDREX, STREX, and SWP.

You can control the alignment requirements of load and store instructions by using the A bit in the CP15 register c1.

## See also

- Technical Reference Manual for your processor

- Aligning data on page 5-25 in the Compiler User Guide

- --unaligned\_access, --no\_unaligned\_access on page 2-128 in the Compiler Reference Guide.

# 2.7.3 Endian support

You can produce either little-endian or big-endian code using the compiler command-line options --littleend and --bigend respectively.

ARMv7-R supports the following endian modes:

LE little-endian format

**BE8** big-endian format.

The ARMv7 does not support the legacy BE-32 mode. If you have legacy code for ARM v7 processors that contain instructions with a big-endian byte order, then you must perform byte order reversal.

The ARMv7-R supports optional byte order reversal hardware as a static option from reset. See the ARM Architecture Reference Manual, ARMv7-A and ARMv7-R edition.

# 2.8 ARM architecture v7-M

This section gives an overview of the RealView tools support for ARMv7-M. Microcontroller profiles implement a programmers' model designed for fast interrupt processing, with hardware stacking of registers and support for writing interrupt handlers in high-level languages. It implements a variant of the ARMv7 protected memory system architecture and supports the Thumb-2 instruction set only.

| Command-line option | Description                                                                                                                                                                                                          |  |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| cpu=7               | ARMv7 with Thumb-2 only and without hardware divide <sup>a</sup>                                                                                                                                                     |  |

| cpu=7-M             | ARMv7 microcontroller profile with Thumb-2 only and hardware divide                                                                                                                                                  |  |

| cpu=name            | <ul> <li>Where <i>name</i> is a specific ARM processor. For example:</li> <li>Cortex-M3 for ARMv7 with Thumb-2 only, hardware divide, ARMv6 style BE8 LE data endianness support, and unaligned accesses.</li> </ul> |  |

a. ARM v7 is not a recognized ARM architecture. Rather, it denotes the features that are common to all of the ARMv7-A, ARMv7-R, and ARMv7-M architectures.

#### 2.8.1 Key features

Key features for ARMv7-M:

- Supports the SDIV and UDIV instructions.

- Uses interrupt intrinsics to generate CPSIE or CPSID instructions that change the current pre-emption priority (see Table 2-10). For example, when you use a \_\_\_disable\_irq intrinsic, the compiler generates a CPSID i instruction, which sets PRIMASK to 1. This raises the execution priority to 0 and prevents exceptions with a configurable priority from entering. See the ARMv7-M Architecture Reference Manual.

| Intrinsic   | Opcode  | PRIMASK | FAULTMASK |

|-------------|---------|---------|-----------|

| enable_irq  | CPSIE i | 0       |           |

| disable_irq | CPSID i | 1       |           |

| enable_fiq  | CPSIE f |         | 0         |

| disable_fiq | CPSID f |         | 1         |

#### Table 2-10 Interrupt intrinsics

Table 2-9 Useful command-line options

# 2.8.2 Alignment support

The data alignment behavior supported by the ARM architecture has changed significantly between ARMv4 and ARMv7. An ARMv7 implementation must support unaligned data accesses. You can control the alignment requirements of load and store instructions by using the A bit in the CP15 register c1.

— Note — \_\_\_\_

ARMv7 architectures do not support pre-ARMv6 alignment.

# 2.8.3 Endian support

You can produce either little-endian or big-endian code using the compiler command-line options --littleend and --bigend respectively.

ARMv7-M supports the following endian modes:

**BE8** big-endian format.

The ARMv7 architecture does not support the legacy BE-32 mode. If you have legacy code for ARM v7 processors that contain instructions with a big-endian byte order, then you must perform byte order reversal. See the *ARM Architecture Reference Manual*.

Developing for ARM Processors

# Chapter 3 Embedded Software Development

This chapter describes how to develop embedded applications with the ARM RealView Compilation Tools, with or without a target system present.

It contains the following sections:

- About embedded software development on page 3-2

- Default compilation tool behavior on page 3-4

- Tailoring the C library to your target hardware on page 3-9

- Tailoring the image memory map to your target hardware on page 3-11

- *Reset and initialization* on page 3-16

- *Target hardware and the memory map* on page 3-22.

# 3.1 About embedded software development

Most embedded applications are initially developed in a prototype environment with resources that differ from those available in the final product. Therefore, it is important to consider the processes involved in moving an embedded application from one that relies on the facilities of the development or debugging environment to a system that runs standalone on target hardware.

When developing embedded software using RealView Compilation Tools, you must consider the following:

- Understand the default compilation tool behavior so that you appreciate the steps necessary to move from a default build to a fully standalone application.

- Some C library functionality executes by using debug environment resources. If used, you must re-implement this functionality to make use of target hardware.

- RealView Compilation Tools has no inherent knowledge of the memory map of any given target. You must tailor the image memory map to the memory layout of the target hardware.

- An embedded application must perform some initialization before the main application can be run. A complete initialization sequence requires code that you implement in addition to RealView Compilation Tools C library initialization routines.

## 3.1.1 Example code

To illustrate the topics described in this chapter, associated example projects are provided in the examples directory, ...\RVDS\Examples\...\emb\_sw\_dev\. Each build is in a separate directory, and provides an example of the techniques described in successive sections of this chapter. Specific information regarding each build can be found in the readme.txt files.

Build 1 is a default build of the Dhrystone benchmark and adheres to the default RealView Compilation Tools behavior. See *Default compilation tool behavior* on page 3-4 for more information.

Build 2 This example adapts build 1 to make use of the Versatile board for clock timing and string I/O. See *Tailoring the C library to your target hardware* on page 3-9 for more information.

Build 3 This example implements a scatter-loading description file to tailor the stack and heap placement.

See *Tailoring the image memory map to your target hardware* on page 3-11 for more information.

- **Build 4** This example can be run standalone on a Versatile board. A vector table and reset handler is implemented. See *Reset and initialization* on page 3-16 for more information.

- **Build 5** This example is equivalent to build 4, but with all target memory map information located in the scatter-loading description file.

See *Target hardware and the memory map* on page 3-22 for more information.

The Dhrystone benchmarking program provides the code base for the example projects. The examples are tailored to run on a Versatile board. However, the principles can be applied to any target hardware. For more information on board connections and settings, see the *Getting Started* section in the *User Guide* for your board.

— Note —

The focus of this chapter is not specifically the Dhrystone program, but the steps that must be taken to enable it to run on a fully standalone system. For further information on the use of Dhrystone as a benchmarking tool, see Application Note 93 - *Benchmarking with ARMulator*<sup>®</sup>. You can find the ARM Application Notes in the Documentation area of the ARM website at http://www.arm.com.

# 3.2 Default compilation tool behavior

When you start work on software for an embedded application, you might not be aware of the full technical specifications of the target hardware. For example, you might not know the details of target peripheral devices, the memory map, or even the processor itself.

To enable you to proceed with software development before such details are known, the compilation tools have a default behavior that enables you to start building and debugging application code immediately. It is useful to be aware of this default behavior, so that you appreciate the steps necessary to move from a default build to a full standalone application.

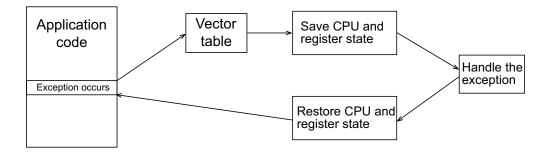

In the ARM C library, support for some ISO C functionality is provided by the host debugging environment at the device driver level. The mechanism that provides this functionality is known as *semihosting*. When semihosting is executed, the debug agent identifies it and suspends program execution. The semihosting operation is then serviced by the debug agent before code execution is resumed. Therefore, the task performed by the host itself is transparent to the program.

See Chapter 8 Semihosting for more information.

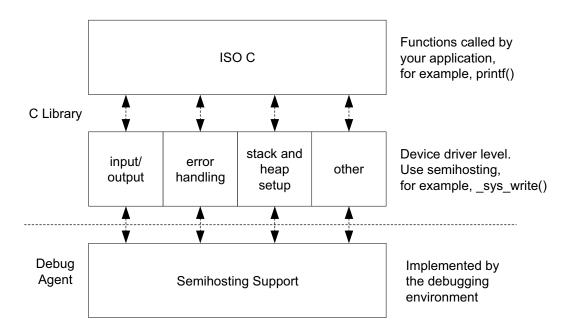

# 3.2.1 C library structure

Conceptually, the C library can be divided into functions that are part of the ISO C standard and functions that provide support to the ISO C standard.

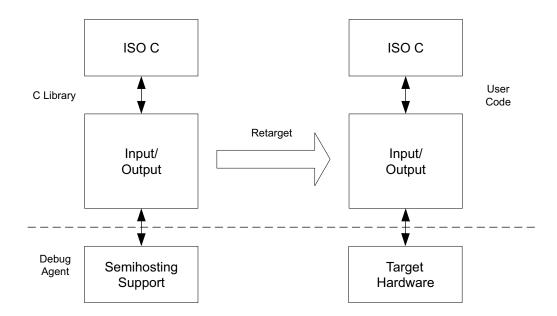

For example, Figure 3-1 on page 3-5 shows the C library implementing the function printf() by writing to the debugger console window. This implementation is provided by calling \_sys\_write(), a support function that executes a semihosting call, resulting in the default behavior using the debugger instead of target peripherals.

# Figure 3-1 C library structure

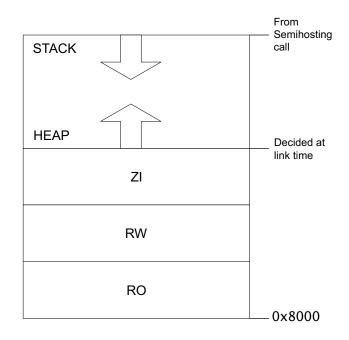

# 3.2.2 Default memory map

In an image where you have not described the memory map, the linker places code and data according to a default memory map, as shown in Figure 3-2 on page 3-6.

—— Note ———

The processors based on ARMv6-M and ARMv7-M architectures have fixed memory maps. This makes porting software easier between different systems based on these processors. See the *Cortex-M1 Technical Reference Manual* and *Cortex-M3 Technical Reference Manual* for more information.

The default memory map is described as follows:

- The image is linked to load and run at address 0x8000. All *Read Only* (RO) sections are placed first, followed by *Read-Write* (RW) sections, then *Zero Initialized* (ZI) sections.

- The heap follows directly on from the top of the ZI section, so the exact location is decided at link time.

• The stack base location is provided by a semihosting operation during application startup. The value returned by this semihosting operation depends on the debug environment.

Figure 3-2 Default memory map

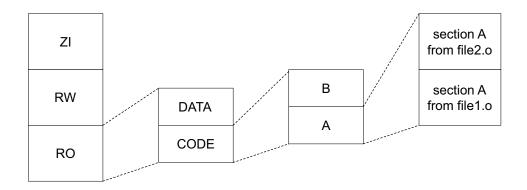

The linker observes a set of rules, shown in Figure 3-3 on page 3-7, to decide where in memory code and data is located. Generally, the linker sorts the input sections by attribute, by name, and then by position in the input list. See *The image structure* on page 3-2 and *Section placement* on page 3-10 in the *Linker User Guide* for more information.

## Figure 3-3 Linker placement rules

For full control of placement of code and data you must use the scatter-loading mechanism. See *Tailoring the image memory map to your target hardware* on page 3-11 for more information.

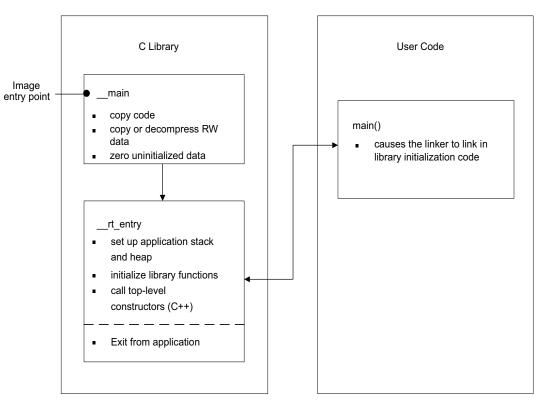

# 3.2.3 Application startup

In most embedded systems, an initialization sequence executes to set up the system before the main task is executed. Figure 3-4 on page 3-8 shows the default RealView Compilation Tools initialization sequence.

#### Figure 3-4 Default initialization sequence

\_\_main is responsible for setting up the memory and \_\_rt\_entry is responsible for setting up the run-time environment.

\_\_main performs code and data copying, decompression, and zero initialization of the ZI data. It then branches to \_\_rt\_entry to set up the stack and heap, initialize the library functions and static data, and call any top level C++ constructors. \_\_rt\_entry then branches to main(), the entry to your application. When the main application has finished executing, \_\_rt\_entry shuts down the library, then hands control back to the debugger.

The function label main() has a special significance. The presence of a main() function forces the linker to link in the initialization code in \_\_main and \_\_rt\_entry. Without a function labeled main() the initialization sequence is not linked in, and as a result, some standard C library functionality is not supported. See --*startup=symbol*, --*no\_startup* on page 2-83 in the *Linker Reference Guide* for more information on using alternative C libraries with a startup symbol different to \_\_main.

# 3.3 Tailoring the C library to your target hardware

By default, the C library uses semihosting to provide device driver level functionality, enabling a host computer to act as an input and an output device. This is useful because development hardware often does not have all the input and output facilities of the final system.

You can provide your own implementation of C library functions that make use of target hardware, and that are automatically linked in to your image in favor of the C library implementations. This process, known as retargeting the C library, is shown in Figure 3-5.

## Figure 3-5 Retargeting the C library

For example, you might have a peripheral I/O device such as an LCD screen, and you might want to override the library implementation of fputc(), that writes to the debugger console, with one that outputs to the LCD. Because this implementation of fputc() is linked in to the final image, the entire printf() family of functions prints out to the LCD.

Example 3-1 shows an example implementation of fputc(). The example redirects the input character parameter of fputc() to a serial output function sendchar() that is assumed to be implemented in a separate source file. In this way, fputc() acts as an abstraction layer between target dependent output and the C library standard output functions.

#### Example 3-1 Implementation of fputc()

```

extern void sendchar(char *ch);

int fputc(int ch, FILE *f)

{ /* e.g. write a character to an LCD screen */

char tempch = ch;

sendchar(&tempch);

return ch;

}

```

In a standalone application, you are unlikely to support semihosting operations. Therefore, you must remove all calls to semihosting functions or re-implement them with non semihosting functions. See *Building an application for a non semihosting environment* on page 2-21 in the *Libraries and Floating Point Support Guide* for more information.

For a full list of C library functions that use semihosting, see Chapter 8 Semihosting.

# 3.4 Tailoring the image memory map to your target hardware

In your final embedded system, without semihosting functionality, you are unlikely to use the default memory map. Your target hardware usually has several memory devices located at different address ranges. To make the best use of these devices, you must have separate views of memory at load and run-time.

Scatter-loading enables you to describe the load and run-time memory locations of code and data in a textual description file known as a *scatter-loading description file*. This file is passed to the linker on the command line using the --scatter option. For example:

armlink --scatter scatter.scat file1.o file2.o

Scatter-loading defines two types of memory regions:

- Load regions containing application code and data at reset and load-time.

- Execution regions containing code and data when the application is executing. One or more execution regions are created from each load region during application startup.

A single code or data section can only be placed in a single execution region. It cannot be split.

During startup, the C library initialization code in \_\_main carries out the necessary copying of code/data and zeroing of data to move from the image load view to the execute view.

# 3.4.1 Scatter-loading description file

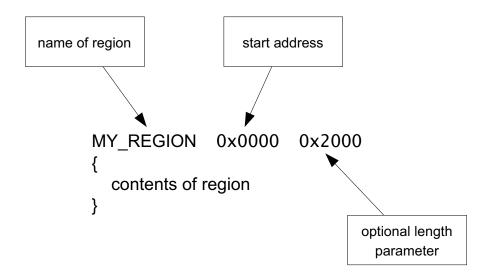

The scatter-loading description file syntax reflects the functionality provided by scatter-loading itself. Figure 3-6 shows the file syntax.

#### Figure 3-6 Scatter-loading description file syntax

A region is defined by a header tag that contains, as a minimum, a name for the region and a start address. Optionally, a maximum length and various attributes can be added.

The contents of the region depend on the type of region:

- Load regions must contain at least one execution region. In practice, there are usually several execution regions for each load region.

- Execution regions must contain at least one code or data section, unless a region is declared with the EMPTY attribute. Non-EMPTY regions usually contain object or library code. The wildcard (\*) syntax can be used to group all sections of a given attribute not specified elsewhere in the scatter-loading description file.

See *Images with a simple memory map* on page 5-6 in the *Linker User Guide* for more examples and information on different memory maps.

See Chapter 3 *Formal syntax of the scatter-loading description file* in the *Linker Reference Guide* for more information on the formal syntax.

# 3.4.2 Root regions

A *root region* is an execution region with an execution address that is the same as its load address. Each scatter-loading description file must have at least one root region.

One restriction placed on scatter-loading is that the code and data responsible for creating execution regions cannot itself be copied to another location. As a result, the following sections must be included in a root region:

- \_\_main.o and \_\_scatter\*.o containing the code that copies code and data

- \_\_dc\*.o that performs decompression

- Region\$\$Table section containing the addresses of the code and data to be copied or decompressed.

Because these sections are defined as read-only, they are grouped by the \* (+R0) wildcard syntax. As a result, if \* (+R0) is specified in a non-root region, these sections must be explicitly declared in a root region using InRoot\$Sections.

See Assigning sections to a root region on page 5-40 in the Linker User Guide for more information.

# 3.4.3 Placing the stack and heap

The scatter-loading mechanism provides a method for specifying the placement of code and statically allocated data in your image. The application stack and heap are set up during C library initialization. You can tailor stack and heap placement by using the specially named ARM\_LIB\_HEAP, ARM\_LIB\_STACK, or ARM\_LIB\_STACKHEAP execution regions. Alternatively you can re-implement the \_\_user\_initial\_stackheap() function if you are not using a scatter-loading description file.

See *Specifying stack and heap using the scatter-loading description file* on page 5-4 in the *Linker User Guide* for more information.

## **Run-time memory models**

RealView Compilation Tools provides the following run-time memory models:

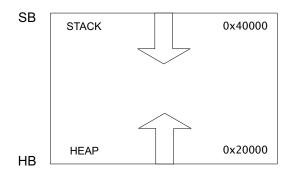

## **One-region model**

The application stack and heap grow towards each other in the same region of memory. See Figure 3-7 on page 3-14. In this run-time memory model, the heap is checked against the value of the stack pointer when new heap space is allocated, for example, when malloc() is called.

#### Figure 3-7 One-region model

Example 3-2 One-region model routine

```

LOAD_FLASH ... {

...

ARM_LIB_STACKHEAP 0x20000 EMPTY 0x20000 ; Heap and stack growing towards

{ }

; each other in the same region

...

}

```

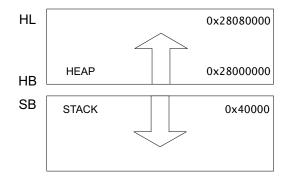

#### **Two-region model**

The stack and heap are placed in separate regions of memory. For example, you might have a small block of fast RAM that you want to reserve for stack use only. For a two-region model you must import \_\_use\_two\_region\_memory.

In this run-time memory model, the heap is checked against the heap limit when new heap space is allocated.

# Figure 3-8 Two-region model

# Example 3-3 Two-region model routine

| LOAD_FLASH<br>{                                                                                 |   |

|-------------------------------------------------------------------------------------------------|---|

| ARM_LIB_STACK 0x40000 EMPTY -0x20000<br>{    }<br>ARM_LIB_HEAP 0x28000000 EMPTY 0x80000<br>{  } | ; |

| }                                                                                               |   |

In both run-time memory models, the stack grows unchecked.

See *Tailoring the runtime memory model* on page 2-69 in the *Libraries and Floating Point Support Guide* for more information.

# 3.5 Reset and initialization

This chapter has so far assumed that execution begins at \_\_main, the entry point to the C library initialization routine. In fact, any embedded application on your target hardware performs some system-level initialization at startup. This section describes this in more detail.

Figure 3-9 shows a possible initialization sequence for an embedded system based on an ARM architecture. If you use a scatter-loading description file to tailor stack and heap placement the linker creates the \_\_user\_initial\_stackheap() function using linker defined symbols for these region names. See *Specifying stack and heap using the scatter-loading description file* on page 5-4 in the *Linker User Guide* for more information. Alternatively you can create your own implementation.

#### Figure 3-9 Initialization sequence

The reset handler is a short module coded in assembler that executes immediately on system startup. As a minimum, your reset handler initializes stack pointers for the modes that your application is running in. For processors with local memory systems, such as caches, TCMs, MMUs, and MPUs, some configuration must be done at this stage in the initialization process. After executing, the reset handler typically branches to \_\_main to begin the C library initialization sequence.

There are some components of system initialization, for example, the enabling of interrupts, that are generally performed after the C library initialization code has finished executing. The block of code labeled SubSmain() performs these tasks immediately before the main application begins executing. See *Using SSuperSS and SSubSS to override symbol definitions* on page 4-18 in the *Linker User Guide* for more information.

#### 3.5.1 The vector table

All ARM systems have a vector table. The vector table does not form part of the initialization sequence, but it must be present for any exception to be serviced. It must be placed at a specific address, usually 0x0. To do this you can use the scatter-loading +FIRST directive, see Example 3-4.

#### Example 3-4 Placing the vector table at a specific address

```

ROM_LOAD 0x0000 0x4000

{

; root region

ROM_EXEC 0x0000 0x4000

{

vectors.o (Vect, +FIRST) ; Vector table

* (InRoot$$Sections)

; All library sections that must be in a

; root region, for example, __main.o,

; __scatter*.o, __dc*.o, and * Region$$Table

}

RAM 0x10000 0x8000

{

; all other sections

* (+RO, +RW, +ZI)

}

}

```

The vector table for the microcontroller profiles is very different to most ARM architectures. For an example of the vector table for your processor, see:

- *The vector table* on page 6-4 for ARMv6 and earlier, ARMv7-A and ARMv7-R profiles

- The vector table on page 6-31 for ARMv6-M and ARMv7-M profiles.

## 3.5.2 ROM and RAM remapping

— Note — \_\_\_\_

This section does not apply to ARMv6-M and ARMv7-M profiles.

You must consider what sort of memory your system has at address 0x0, the address of the first instruction executed.

\_\_\_\_\_Note \_\_\_\_\_

This section assumes that an ARM processor begins fetching instructions at 0x0. This is the norm for systems based on ARM processors. However, some ARM processors can be configured to begin fetching instructions from 0xFFFF0000.

There has to be a valid instruction at 0x0 at startup, so you must have nonvolatile memory located at 0x0 at the moment of reset. One way to achieve this is to have ROM located at 0x0. However, there are some drawbacks to this configuration.

Example 3-5 shows another solution implementing ROM/RAM remapping on reset. The constants shown in this example are specific to the Versatile board, but the same method is applicable to any platform that implements remapping in a similar way. Scatter-loading description files must describe the memory map after remapping.

#### Example 3-5 ROM/RAM remapping

```

; --- System memory locations

EOU 0x101E0000 : Address of control register

Versatile ctl req

DEVCHIP_Remap_bit

EQU 0x100

; Bit 8 is remap bit of control register

FNTRY

: Code execution starts here on reset

; On reset, an alias of ROM is at 0x0, so jump to 'real' ROM.

pc, =Instruct_2

I DR

Instruct 2

; Remap by setting remap bit of the control register

; Clear the DEVCHIP_Remap_bit by writing 1 to bit 8 of the control register

LDR

R1, =Versatile_ctl_reg

LDR

R0, [R1]

ORR

R0, R0, #DEVCHIP_Remap_bit

STR

RØ. [R1]

: RAM is now at 0x0.

; The exception vectors must be copied from ROM to RAM

: The copying is done later by the C library code inside __main

: Reset Handler follows on from here

```

#### 3.5.3 Local memory setup considerations

Many ARM processors have on-chip memory management systems, such as MMUs or MPUs. These devices are normally set up and enabled during system startup. Therefore, the initialization sequence of processors with local memory systems requires special consideration.