OpenRISC—OR1200子模块QMEM

1. QMEM的作用

QMEM是Quick Memory的简称,顾名思义,就是快速存储器,实际上这是一个片上RAM,可以实现在一个时钟内读取其中存储内容(指令、数据),用户可以把一些常用的代码存放在其中,比如:Context切换过程、异常处理句柄、堆栈等。

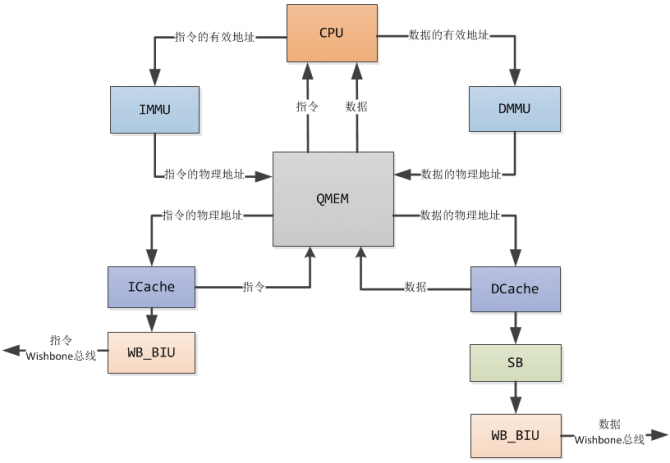

CPU取指、加载/存储数据过程,如下图所示:

(1)取指令过程

CPU给出指令的有效地址(EA:Effective Address),IMMU将有效地址翻译为物理地址(PA:Physical Address),然后送到QMEM中。

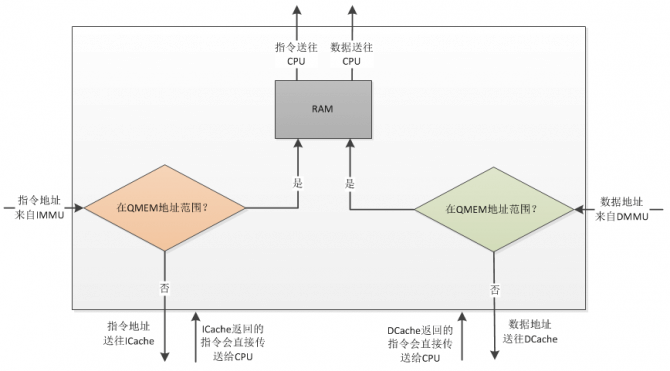

QMEM判断该地址是否位于QMEM的地址范围内,如果是,就直接取出指令送到CPU;如果不是位于QMEM的地址范围内,则将该地址发送给ICache。

ICache查看该地址是否被缓存,如果是就直接读出指令送往QMEM,QMEM直接转给CPU;如果ICache没有命中,则通过指令WB_BIU模块访问外部存储器获取指令。

(2)加载/存储数据过程

CPU给出读写数据的有效地址,DMMU将有效地址翻译为物理地址,然后送到QMEM中。

QMEM判断该地址是否位于QMEM的地址范围内,如果是,就直接读写指定地址;如果不是位于QMEM地址范围内,则将该地址发送给DCache。

DCache查看该地址是否被缓存,如果是就直接将该数据发送给QMEM,后者直接转发给CPU或者直接写数据;如果DCache没有命中,则会通过SB、数据WB_BIU模块访问外部存储器读写数据。

(3) QMEM的作用示意图

2. QMEM模块的连接

2.1 Wishbone总线的分布

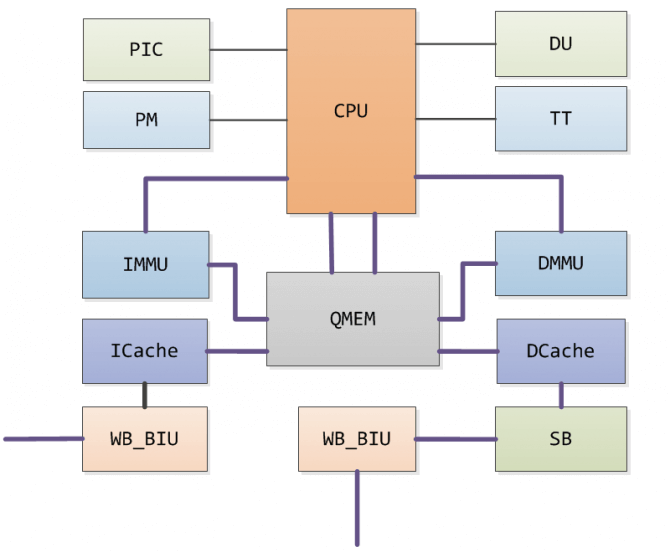

上一篇《OpenRISC—OR1200总线标准Wishbone》介绍了Wishbone总线。事实上,OR1200内部大量使用到Wishbone总线,比如:CPU模块与IMMU、IMMJU与QMEM、QMEM与ICache、ICache与WB_BIU之间均使用到了Wishbone总线规范。

从OR1200_TOP角度看各子模块,wishbone总线分布如下图所示(图中加粗的紫色线条表示Wishbone总线规范,且均为点对点互连):

2.2 QMEM和其它模块的连接

关于QMEM具体总线的连接方式,此处不再一一列举,请查看附件 ![]() or1200_top.png 如下:

or1200_top.png 如下:

参考来源:

[1] 《步步惊芯—软核处理器内部设计分析》 雷思磊 电子工业出版社