电源纹波测试及问题探讨(一)

测试工况。

输入电压:12V 输出电压:3.3V

示波器型号:Agilent DSO-X 2022A 采样率2GSa/s,带宽200MHz

电路原理图:

C3:50V/100uF直插铝电解电容 C1:22uF 1206封装陶瓷电容 C2:6.3V/10uF3216封装钽电容 C4:0.1uF 0402封装陶瓷电容

原理:12V来自电源适配器,内部是一个开关电源。先经过7805降压后得到5V电压,再经过一片LDO降压得到3.3V电压输出,示波器探头接在3.3V和GND

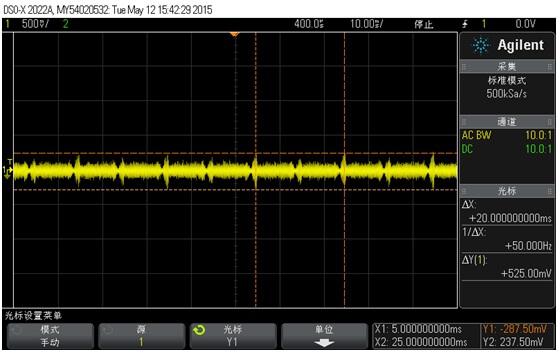

测试条件1

不接C2、C4,即LD1117DT33直接输出3.3V给示波器测量。带宽限制:开

为何要开带宽限制?因为我们此处讨论的是电源本身的纹波特性,对于更高频率的干扰信号,并不是由电源本身产生,而应归结为测量时引入或板级设计不合理而引入的干扰,并不在电源纹波的讨论范围内。

纹波测试:

分析:即便是LDO,如果输出不接滤波电容,其纹波也会很大,笔者所测得的纹波高达数百毫伏(图中所示峰峰值为525mV),且低频纹波十分明显,上图中两个尖峰的时间间隔为20ms,换算成频率为50Hz,这应该是电网混入的杂波,也叫AC噪声,在两个尖峰的中间位置还有一个小尖峰,如果把这个小尖峰也算进去,就可以称作整流纹波,之前搭过全波整流的人都知道,电网的50Hz交流电经过全波整流以后会得到100Hz的脉动直流,相当于把负半周期的信号也叠加进来了。

结论:LDO也不是绝对安静的,因为在很多实际应用场合,电路板最初输入的电源都是开关电源,即便在板上采用LDO来对芯片进行供电,如果不重视电源端的滤波处理,系统内部则会引入极大的噪声。而数字IC的IO端口电平是由电源决定的,如果电源纹波过大,就有可能会导致数据错误、丢包等现象。

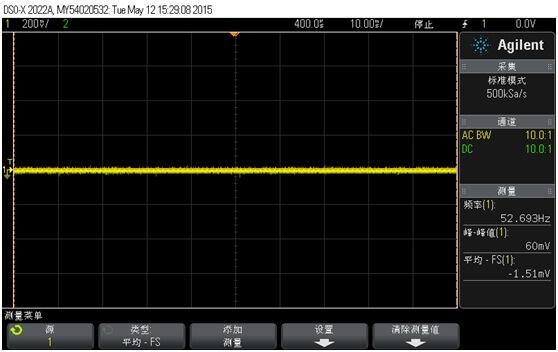

测试条件2

输出端并联一个10uF钽电容到GND。带宽限制:开 示波器设置同上

纹波测试(低频):

分析:奇迹出现了,仅仅是并接了一个小小的电容,就能让电源纹波几乎消失,从上图可以看出,电网混入的50Hz AC噪声几乎消失殆尽,峰峰值只有60mV。

结论:LDO输出端并接适当容量的电容能达到显著的滤波效果。

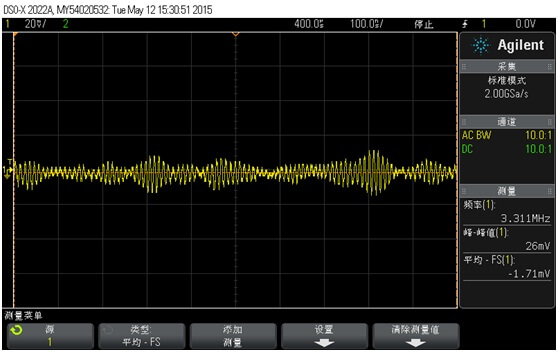

纹波测试2(高频):

分析:并联了10uF钽电容后,电源纹波主要集中在了高频段。众所周知,实际的电容并不是理想电容,存在损耗因素,包括ESR和ESL,随着频率的升高,电容会达到一个谐振点,在这点附近,电容滤波效果最好,因为在这一点上,电容的等效阻抗最低,能够给该频段的纹波信号一个很好的对地通路,从而起到旁路的效果,随着频率进一步升高,电容的特性会越来越接近一个电感,从而逐渐失去滤波效果。实际经验表明,电容的容值越大,ESR和ESL会越大。通常,同等容值的钽电容比陶瓷电容的ESR更大(也正因为这一点,钽电容反而更适合做LDO输出端的滤波,至于为什么,国半有篇文章专门讨论这个问题,有兴趣的可以败毒google或向我要)

试想,如果再并联一个更小的电容,会有什么效果呢?

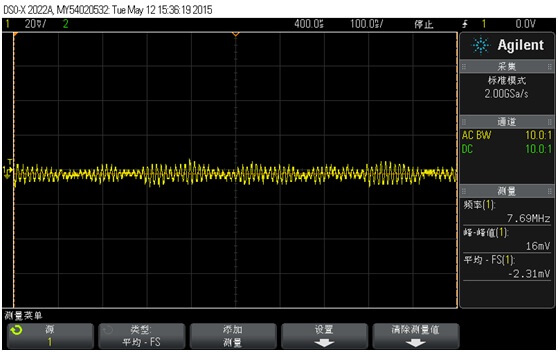

测试条件3

在10uF钽电容两端再并联一个0.1uF的无极性电容。 其他条件同2

分析:由上图可知,纹波进一步减小(虽然不如2那么明显),之前是20几个毫伏,现在只剩16毫伏,且纹波集中在了更高的频段。

结论:小电容对高频纹波可以起到更好的抑制作用。

结语:电源供电部分是板级硬件设计的重中之重,根据笔者仅有的经验,电路板上的很多问题,电源供电不正常而导致的占了一大半。尤其是当板上有敏感的模拟器件时,更要注意电源纹波所带来的负面影响并想办法减小这种影响。对电源端增加滤波电容确实应当成为一个习惯,这样可以避免一些完全没有必要的奇怪问题。此外,笔者此次测试的条件均为空载。实验结果仅供参考,因为实际的应用系统里,负载是千变万化的,比如容性负载、开关型器件等,分析起来会更加复杂。电源有很多问题值得深入探讨,后续笔者会在有空时针对更加复杂的工况做进一步的测试。