PL2302 串口信息:

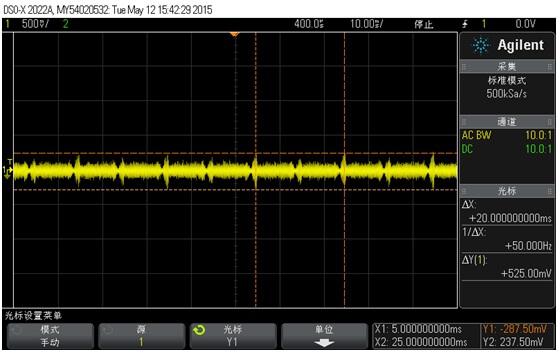

电源设计在硬件设计中占据着很重要的地位,除了精度以外,电源纹波是最值得关注的问题。相比于开关电源,传统的线性稳压源纹波更小。目前低压差线性稳压器(LDO)在很多应用中都能见到其踪影。而低压差线性稳压器(LDO)是不是绝对安静的呢?笔者为此做了个简单的实验

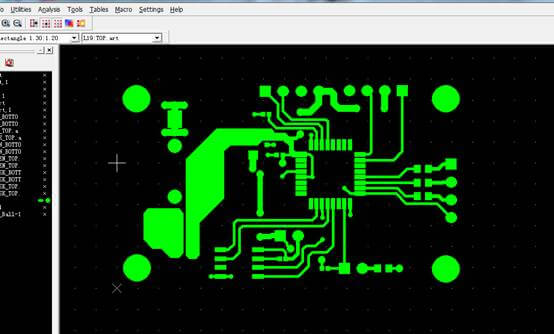

Allegro版本:16.6 CAM350:9.5 在用allegro导gerber的时候,碰到一个问题,就是在allegro中生成光绘后,用CAM350导入,无法显示板框,如图所示。

板框无法显示(TOP层) 查了一下光绘的设置,我确实在TOP层添加了OUTLINE(如图2),但为什么就是...

硬件实现乘法运算有好几种:

1、最原始的就是移位相加,最经济,但速度慢。

2、组合逻辑乘法器,也叫并行乘法器,直接将每一种结果枚举然后通过查表 算结果,这种方式理论上最快,但很占资源,并且由于大量使用组合逻辑,在实际的FPGA实现时,会导致逻辑延迟较大,速度很难做得很快。

3、折中方案,例如: 流水线、加法树乘法器。在组合逻辑中间插入时序单元,因为FPGA内部触发器资源相对较为丰富,而组合逻辑资源,也就是查找表资源则比较宝贵,所以需要 充分利用FPGA内部的时序单元,这样虽然会多了几个周期,但是最高支持的时钟频率Fmax(这个Fmax是搞FPGA设计时所需要用到的一个很重要的参 数)会提高,整体速度自然也会得到弥补。

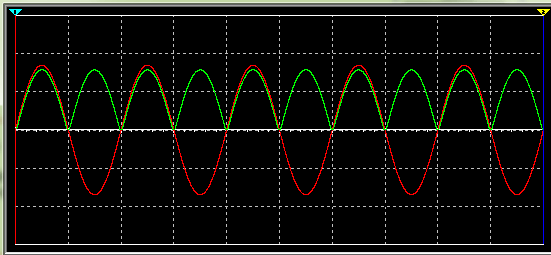

仿真效果如下: